# cover story/cover story/cover story/cover story/cover story/cover

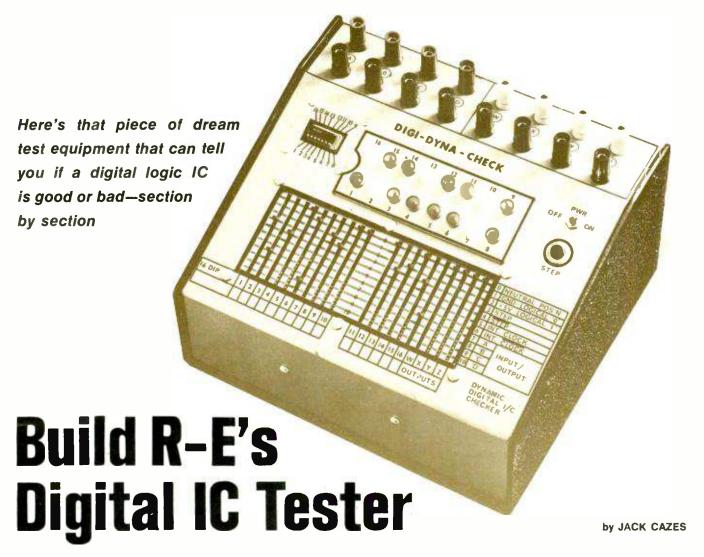

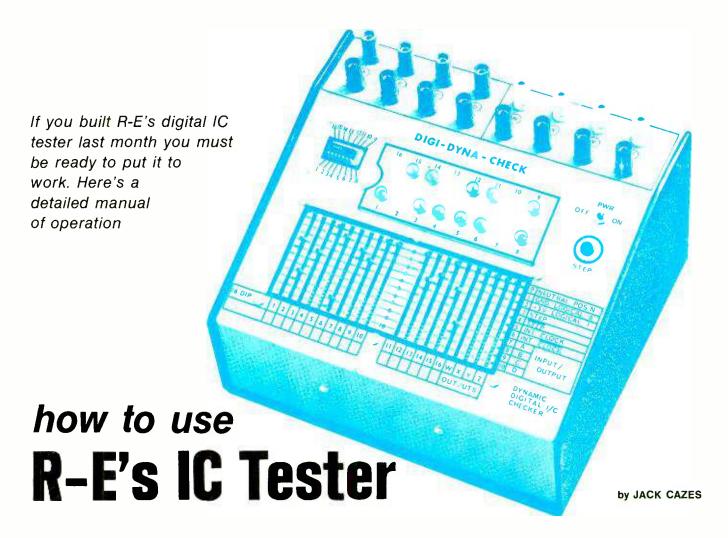

HAVE YOU EVER WISHED YOU HAD A fast, easy way to test the surplus digital IC's in your spare parts collection? Have you wanted to check an IC in-circuit, under actual operating conditions? Wouldn't it be great to be able to monitor the logic states at several points on a digital circuit board . . . even supply power to the board from an external source?

The DIGI-DYNA-CHECK is a truly dynamic digital integrated circuit checker that can be used to test digital IC's under actual operating conditions; it can be made to perform just as though it were functioning in an actual circuit. Tests can be performed both inand out-of-circuit. A 5-volt regulated supply, capable of delivering up to 1 amp, is available within the DIGI-DYNA-CHECK to "fire up" fifteen or more IC's on a circuit board via an adapter cable with its miniature IC connecting clip.

An internal "bounceless" pushbutton, mounted on the front panel, can be used to advance counters, dividers, shift registers, etc., one step at a time. If desired, such IC's can be put through their paces automatically at a rate suitable for observing with an oscilloscope. This automatic mode of operation is available via an internal 50-kHz conditioned clock with complementary outputs.

Connections to "the outside world", ie., to equipment external to the DIGI-DYNA-CHECK, such as a scope, other voltage sources, oscillators, etc., are easily made via eight 5-way binding posts mounted on the front panel. Any internal or externally available function can be patched to any pin or combination of pins on the integrated circuit under test by means of the matrix programmer in the DIGI-DYNA-CHECK.

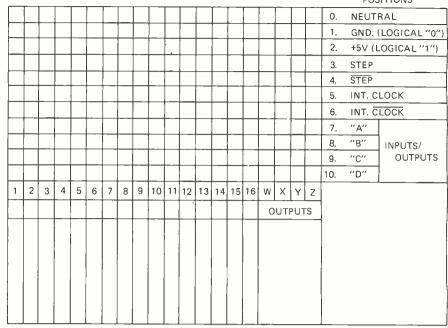

The heart of the checker is a 20-slider by 10-position matrix switch that is used to program the internal and/or external functions and logic levels for the IC under test. Another article will describe, in great detail, the programming and test procedures employed for a variety of digital integrated circuit types.

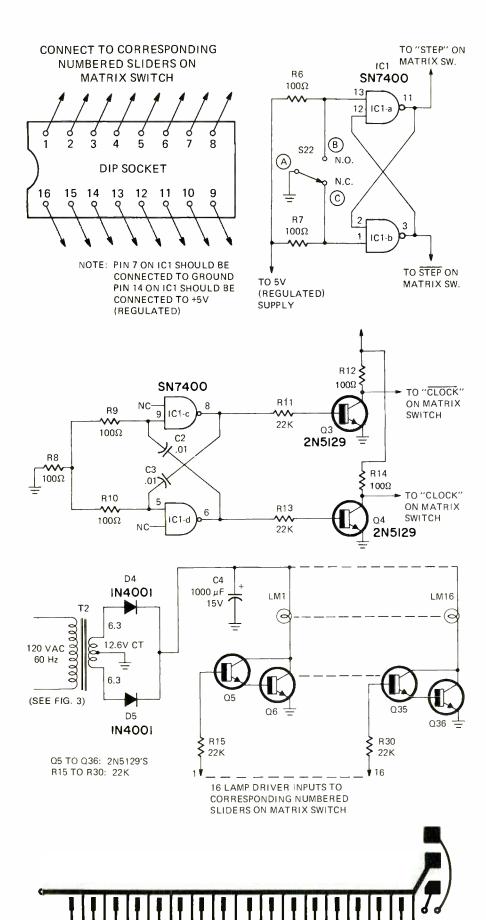

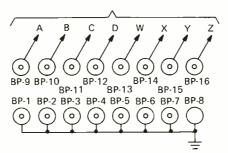

A schematic of the matrix switch used in the DIGI-DYNA-CHECK is in Fig. 1. It shows the connections between the various functions and the pins of the IC being tested. Basically, it consists of twenty 10-position slide switches mounted together in a single frame, with corresponding positions on all switches wired together. Thus, when two or more sliders are in the same position, they are connected internally. Additionally, each slider has a "home" or neutral position (no connection to any other slider).

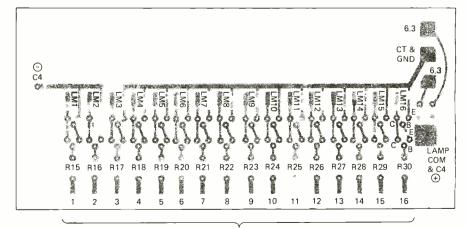

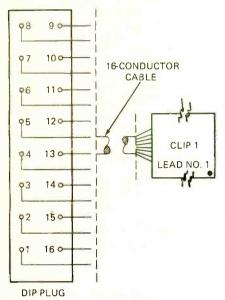

The first sixteen sliders are con-

nected to the correspondingly numbered pins of a 16-pin DIP (see Fig. 2) IC test socket and to sixteen lampdriver assemblies used to monitor logic levels present at all sixteen IC pins simultaneously. The remaining four sliders, marked W, X, Y, and Z in Fig. 1. are wired to four similarly marked 5way binding posts. Six of the matrix positions are connected internally to ground (logical 0), +5 volts (logical 1), the two complementary "step" functions, and the two complementary "clock" functions. The remaining four matrix positions are brought out to 5way binding posts marked A, B, C, and D. This provides a 4 X 4 matrix (ABCD by WXYZ) that can be used for making a variety of special test connections, both internal and external to the DIGI-DYNA-CHECK.

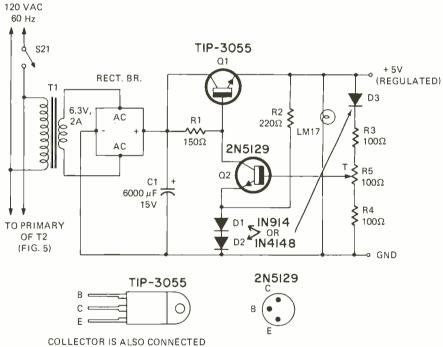

Two power supplies are built into the checker. A regulated, highly filtered 5-volt supply capable of delivering up to 1 amp, continuously, is used to power the internal step and clock circuits (Fig. 4), and to supply V<sub>cc</sub> and logic 1 level voltage to the integrated circuit under test. The regulated supply can also be used to provide power to a board containing many IC's for in-circuit tests. A filtered, but unregulated 5-volt supply provides power to the lamps and their

PARTS LIST All resistors 1/2-watt 10% unless noted

R1-150 ohms

R2-220 ohms R3. R4-100 ohms

R5\_100 ohms, Trimpot R6, R7, R8, R9, R10, R12, R14—100 ohms, ¼ watt

R11, R13, R15 thru R30-22,000 ohms, 1/4 watt

C1-6000  $\mu$ F, 15V, electrolytic C2, C3-0.01  $\mu$ F, 100V

C4-1000 µF, 15V, electrolytic D1, D2, D3-1N914 or 1N4148

D4, D5-1N4001 or similar (1A, 50V)

Rectifier Bridge-full wave, 1A, 100V PIV

IC1-SN-7400 (quad 2-input NAND gates) BP1 thru BP16-5-way binding posts, insulated

LM1 thru LM7-4V, 50mA miniature lamp as-

sembly

Q1-TIP-3055

Q2 thru Q36-2N5129

Matrix Switch (S1 thru S20)-20-pole 10-position (Part C10-42A, Cherry Electric Co., 1650 Old Deerfield Road, Highland Park, Ill. 60035)

S21-spst miniature toggle

\$22-spdt miniature toggle Miscellaneous parts:

16-pin DIP test sockets (2)

16-pin DIP test plug

16-pin DIP test clip

16-lead ribbon cable (21/2 feet)

PC board

Perf board with 0.1-inch hole spacing

Heat sink for TIP-3055 transistor

Case

FIG. 1 (top)-MATRIX SWITCH layout. See cover photo for 14- and 16-pin DIP settings. FIG. 3-POWER SUPPLY for 5 volts regulated to step and clock circuits and the IC under test. FIG. 7-b (right)-PARTS LAYOUT for lampdriver board. The C-B-E terminals at right are for Q35 and Q36. Transistor pairs Q5-Q6 through Q33-Q34 are positioned from left to

SLIDERS

COLLECTOR IS ALSO CONNECTED TO MOUNTING TAB

THESE DRIVER INPUTS ARE CONNECTED TO THE CORRESPONDING NUMBERED SLIDERS ON THE MATRIX SWITCH.

associated driver circuits. This is shown in Fig. 5.

The stepping circuit is merely an electronic contact bounce eliminator. Solid metal switch contacts are inherently noisy and must be conditioned when used with high-speed solid-state circuits. An s.p.d.t. momentary pushbutton switch (S22 in Fig. 6) is connected to a basic NAND gate memory circuit. In the position shown, the output of ICl-a is at logical 0 level, while that of IC1-b is a logical 1. Noisy, multiple contacts with C, as the switch moves toward B, has no effect on the outputs; the gates cannot change state until gate 1-a input is at 0 level. This occurs only at the time when the switch first contacts B. The output of ICI-a then swithces over to 1 and output of IC1-b switches over to 0. Once these levels have been established in the manner described, they are not affected by further "make" and "break" movements of the switch (contact bounce) at B. Complementary outputs are available from this circuit. The STEP output is initially at logical 0 and produces a fast rise transition to logical 1 and then rapidly back to 0 when the pushbutton is depressed and released. The converse is true for the STEP (called NOT STEP) output. Both of these complementary functions are useful for testing digital IC's.

The clock circuit shown in Fig. 4 is an astable multivibrator made up of the two remaining NAND gates of IC1 (an SN-7400). The values of the gate inputsinking resistors (R8, R9, and R10) were chosen to maintain the gate input levels near the logic threshold. In this way, as C2 and C3 charge and discharge, the gate input levels oscillate above and below the threshold level. This results in the gate outputs oscillating in a complementary manner. The frequency of oscillation is determined primarily by the values of C2 and C3 according to the equation

Frequency =  $\frac{1}{2(R8 + R9) \cdot C}$

where C = C2 = C3 and R9 = R10. The component values shown in Fig. 4 result in a frequency of approximately 50 kHz. Some fine adjustment can be made by varying R8. A pair of transistor amplifiers (Q3 and Q4) is used at the complementary outputs to provide more than adequate power to drive sev-

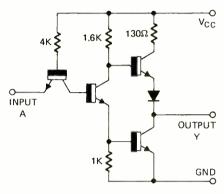

FIG. 2 (top left)—IC SOCKET TERMINALS are wired to matrix switches on instrument panel. FIG. 4 (second from top)—INTERNAL CLOCK is a free-running multivibrator. FIG. 5 (third from top)—LAMP DRIVERS are Darlington pairs to reduce loading on IC under test. FIG. 6 (top right)—STEP SWITCH with electronics added to eliminate effects of contact bounce. FIG. 7-a (left)—FOIL PATTERN for lamp driver. Enlarge so foil is 7½ inches across at widest point.

eral IC loads simultaneously. This is especially important where in-circuit testing is to be performed on a board that contains a multiplicity of IC's.

Sixteen lamp readouts continuously monitor the logic condition simultaneously at all pins of an IC under test. A voltage level above approximately 1.4 volts will cause a lamp to turn on, indicating a logical 1 level. Darlington-pair transistor amplifiers are employed as lamp drivers so that the IC under test cannot be overloaded by the lamp monitors. The selection of 1.4 volts as the threshold level permits the lamps to indicate properly logic levels for most RTL. DTL. TTL. and MOS digital integrated circuits. However, see the second article in this series for special precautions involving RTL IC tests. The lamp-driver circuits are shown in Fig. 5.

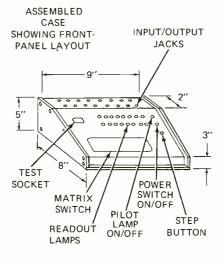

#### Mechanical construction

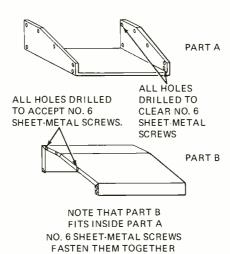

The author's prototype of the DIGI-DYNA-CHECK was assembled in the home-made sloping-front aluminum case shown in Fig. 8. Although case design and front-panel layout are not essential to the proper functioning of the tester, the arrangement shown offers convenience in use. Alternatively, a commercially available box of any design can be used, provided it is large enough to house all of the components.

Drill and punch the front panel to accept those components that will be mounted directly to it. These include the DIP test socket, the matrix switch, the readout lamps, pilot lamp and power switch, step button, and the 5way binding posts. Rectangular openings can be cut out either with a nibbling tool or with a Bernz cutter. Several holes will also have to be drilled in the rear apron of the case to accommodate the line cord with its strain relief bushing. the two power transformers, and two pairs of L-brackets for the two circuit boards containing the lamp drivers, the 5volt supplies, and the STEP and CLOCK circuits. The case can now be painted and lettering applied. Dry-transfer letters are particularly well suited for this job. It makes the checker more convenient to use if two different colors are used to number the test socket, lamp readouts, and matrix sliders to differentiate between the leads of 14-pin and 16-pin DIP integrated circuits as shown in the cover photo.

All components except the two circuit boards can now be mounted in the case.

#### Wiring the tester

The two circuit boards should be prepared and wired first. Then put them aside until all other wiring has been completed. Either copper-clad PC boards or perforated board construction can be used, as wiring layout is not criticial. The foil pattern in Fig. 7-a corresponds to the schematic for the lamp

drivers. Since there are sixteen identical driver circuits involved, the handwiring approach would be tedious here. This foil pattern also includes the unregulated 5-volt supply of Fig. 5. The ac input to this board is from the secondary of T2, mounted at one end of the rear apron next to T1. Do not connect the power to this board until it is ready to be mounted to the case. Connect one end of a 16-lead cable to the sixteen inputs of the driver circuits on this board. Number the leads at the other end of

FIG. 8—SLOPING-FRONT INSTRUMENT CASE, its dimensions, construction and how the two parts are fitted and joined together.

CONNECT TO CORRESPONDING MARKED TERMINALS ON MATRIX SWITCH

FIG. 9—BINDING POSTS are mounted across the top of the case and connected to the matrix circuitry as indicated.

this cable. They will be connected later to the matrix switch.

Next, prepare the board containing the regulated 5-volt supply and the STEP and CLOCK circuits. A perforated board with 0.1 inch hole spacings was used in the author's model. This hole spacing readily accommodates the pins on the socket into which IC-1 will be inserted. Follow the schematics in Figs. 2, 3, and 4, making certain that all +5-volt points are tied together, and all grounds are tied together. Wire the line cord, pilot lamp, power switch, and transformer primaries as shown. Now plug IC-1 into its socket.

The 5-way binding posts (BP1 to BP16) should now be wired according to Fig. 9. The ground bus joining BP1 thru BP8 should be connected to matrix switch position 1. The remaining eight binding posts can then be connected to their respective sliders (W thru Z) and positions (A thru D) on the matrix switch.

Connect one end of a 16-lead cable to the sixteen contacts of the DIP test socket. Number the leads at the other end of the cable to correspond with the socket contacts. This end will be wired later to the matrix switch together with the correspondingly numbered leads on the cable that was previously connected to the lamp driver board.

Wire the miniature lamps (mounted on the front panel) to the sixteen output pads on the driver board. One lead from each lamp should be connected to a common +5-volt tie point on the board. This board can now be mounted to the rear apron of the case with two L-brackets. Connect the secondary leads from T2 to the proper locations on the board.

Connect the two 16-conductor cables (from the DIP test socket and from the lamp driver board) to the matrix switch. Be sure that all leads go to correspondingly numbered *sliders* on the matrix switch. Thus, the lead from pin No. 1 on the test socket and the lead from input No. 1 on the lamp driver board should both be connected to *slider* No. 1 on the matrix switch, etc.

The perf-board can now be mounted on the rear apron of the case, just above and parallel to the driver board. Solder the secondary leads from T1 to the perf-board. Now, connect the +5-volt (regulated), ground, clock, clock, step, and step outputs from the perf-board to their respective position terminals on the matrix board.

Finally, connect the ground terminal from the lamp driver board to the ground terminal on the matrix switch (position 1).

Construct an adapter cable as shown in Fig. 10. This will be used for in-circuit testing of integrated circuits.

(continued on page 85)

(continued from page 36)

**Testing**

Plug the Digi-Dyna-Check into a 120-volt, 60-Hz supply and turn on the power switch. Adjust R5 on the perfboard to obtain exactly 5 volts at the output of the regulated power supply. This should be measured with a

FIG. 10-ADAPTER CABLE consists of 16-pin plug and clamp and is used for in-circuit testing of DIP-type integrated circuits.

VTVM, an FET input voltmeter, or other similar high input-impedance device. With all matrix sliders in the neutral position, only the pilot lamp should be on. Move sliders 1 thru 20 to position 1 (ground). None of the lamps should light. All IC test socket pins and binding posts W thru Z should be shorted together and at ground level. (Check with an ohmmeter). Move all sliders to position 2 (+5V). All sixteen readouts should be on. All DIP test socket pins and binding posts W thru Z should be at +5-volts. Move all sliders to position 3 (Step). All socket pins should be at logical 0 together with binding posts W thru Z. Depressing the STEP button should cause all lamps to turn on and bring all socket pins and binding posts W thru Z to logical I. Releasing the STEP button should return everything to their initial states. Move all sliders to position 4 (Step). Everything should behave as the inverse of that described for position 3. Move all sliders to position 5 (Clock). All lamps should glow at half brilliance due to the 50% duty cycle of the square wave clock output. A 50 kHz square wave should be present at all DIP test socket pins and at binding posts W thru Z. With all sliders at position 6 (Clock) you should see the inverse of that observed for position 5. Wave forms in positions 5 and 6 can be observed with a scope at binding posts W thru Z. Moving any of the sliders to any of the four positions 7 thru 10 should connect their corresponding circuits to binding posts A thru D, respectively.

If everything described here checks out A-OK, you're ready to use your Digi-Dyna-Check to check IC's.

#### **BUILD A SOLID-STATE LASER**

Our June cover feature presents complete construction details of a solid-state laser. It's both easy and inexpensive to build. If you've been waiting for a low-cost low-power "safe" laser to experiment with you won't want to miss the June issue of Radio-Electronics.

If you don't do it, It won't get done

# TV TUNER SERVICE

## You owe it to yourself

to try P.T.S. We are the fastest growing, oldest and now the largest tuner service company in the world. Here is what you get.

- Fastest Service—8 hr.—in and out the same day. Overnight transit to one of our six plants, for parts, tuners or IF-modules.

All tuners cleaned inside and out, repaired, realigned and air tested.

On IF-modules all stages checked, all traps set with high calibre test equipment.

Fine Quality! Your customers are satisfied and you are not bothered with returning your units for rework! you are not bothered with returning your units for rework!

5. Lower Cost! Up to \$5.50 less than other tuner

- 6. Friendly, helpful personalized service!

### 1 YEAR GUARANTEE

FIRST TO OFFER 365-DAY GUARANT COLOR—BLACK & WHITE—TRANSISTOR T ALL MAKES GUARANTEED COLOR ALIGNMENT— NO ADDITIONAL CHARGE GUARANTEE!

LIKE TO DO IT YOURSELF?

PTS makes all tuner parts available to you.

Send one dollar (redeemable) for our TUNER RE-PLACEMENT GUIDE AND PARTS CATALOG

60 pages of top information

60 bages of top information

60 bages

60 bages

# We offer you finer, faster...

Precision uner Service VHF-UHF-FM UV-COMBO

\$ 9.95

IF-MODULE

\$12.50

Major Parts charged at Net Price

CUSTOMIZED REPLACEMENTS AVAILABLE FOR \$12 95 UP (NEW OR REBUILT)

For fastest service; send faulty unit with tubes, shields and all broken parts to

### PTS ELECTRONICS, INC.

HOME OFFICE-SOUTHEAST— WEST COAST— SOUTHWEST-

P.O. Box 272—Bloomington, Ind. 47401 P.O. Box 6771—Jacksonville, Fla. 32205 P.O. Box 41354—Sacramento, Calif. 95841 P.O. Box 3189—Springfield, Mass. 01103 P.O. Box 7332—Longview, Tex. 75601 P.O. Box 4145—Denver, Colo. 80204

Tel. 812/824-9331 Tel. 904/389-9952 Tel. 916/482-6220 Tel. 413/734-2737 Tel. 214/753-4334 Tel. 303/244-2818

Circle 67 on reader service card

MAY 1972 ● RADIO-ELECTRONICS 85

NOW THAT YOU'VE COMPLETED THE construction of your DIGI-DYNA-CHECK (Radio-Electronics, May 1972), let's see how it can be used for both in- and outof-circuit testing of a wide variety of digital integrated circuits. By simulating actual operating conditions for the unit under test; the DIGI-DYNA-CHECK performs a functional check of an ic under truly dynamic conditions. Operating power is supplied (+5 volts at 1 amp, regulated), where necessary and logic levels are readily applied to the inputs of the IC under test. All input and output logic levels are monitored, simultaneously, with a bank of sixteen indicator lamps, a lighted lamp representing a 1 logic state. A lamp that is off is indicative of either a 0 logic state or an indeterminate condition that is possible when there is no connection at that test

Gates of all types can be put through their paces by checking the output levels that result from various combinations of input levels. Flip-flops, counters, and shift-registers are advanced through their various states either stepwise (manually), or continuously (automatically) at a frequency of approximately 50 kHz, a rate that can be easily observed with most commonly used oscilloscopes.

Before we get into the actual exam-

ples of test procedures that can be used with different types of digital IC's, let's take a closer look at the matrix switch to learn the how and why of its operation. Since it's the heart of the DIGI-DYNACHECK, a thorough understanding of its operation is necessary.

The matrix switch consists of twenty 10-position slide switches, each having, in addition to ten *common* positions, a neutral or "no connection" position. The first sixteen sliders are wired to correspondingly numbered pins of the DIP (Dual-Inline Plastic) test socket and to the inputs of sixteen lamp indicators. The remaining four sliders are brought out to four binding posts marked W, X, Y, and Z.

Each of the ten switch positions is wired, internally, in common, for all 20 switches, to the following functions. See Table I on next page.

Looking at Table I, we see that any number of the sixteen IC contacts as well as binding posts W, X, Y, and Z can be connected to any of the six internally available functions by merely moving their corresponding matrix sliders to the positions representing the desired functions. Since all switches have their identically numbered positions wired in-common (bussed together), two or more sliders resting on the same numbered positions will result in their

IC terminals and/or binding posts being connected together. Sliders W through Z and positions A through D form a 4 × 4 matrix with their eight binding posts which, as we shall soon see, can be useful in connecting the test IC to the outside world-to a scope, external power supplies, resistors, capacitors, test leads, etc. When any or all of the sliders W through Z are in positions 1 through 6, the corresponding internal functions are available for external use. This can come in handy when checking external circuitry. Note that when sliders 1 through 16 are in positions A through D, the corresponding monitor lamp inputs are automatically connected to the external binding posts.

Thus, for example, with slider 1 in position A, and test leads plugged into binding post A and ground, lamp 1 can be used as a logic level test probe for checking relative logic levels on PC boards at locations other than at IC terminals.

The numbering system for DIP integrated circuits is illustrated below. Very often, there is some sort of mark, such as a dot or a number 1 at pin 1. However, even in cases where there is none. pin 1 will always be at the notched end of the IC package as shown in Fig. 1. The remaining pins are numbered counting counterclockwise.

| POSITION | TABLE I WIRED TO                                              |

|----------|---------------------------------------------------------------|

| 0        | No connection (Neutral)                                       |

| 1        | Ground (to provide circuit common and logical 0)              |

| 2        | + 5V, regulated (to provide circuit power and logical 1)      |

| 3        | STEP (via manual stepping button)                             |

| 4        | STEP (complement of position 3)                               |

| 5        | INT CLOCK (internally available 50 kHz square-wave generator) |

| 6        | INT CLOCK (complement of position 5)                          |

| 7        | Binding post A                                                |

| 8        | Binding post B                                                |

| 9        | Binding post C                                                |

| 10       | Binding post <b>D</b>                                         |

FIG. 1—FINDING PIN 1 of a dual-inline-package (DIP) IC is easy. Just look for the notch in one end as shown here.

#### In-circuit testing

To test IC's in-circuit plug the incircuit adapter cable into the test socket of the DIGI-DYNA-CHECK and connect the test clip at the other end of the cable to the IC to be checked. Be sure that the clip is properly oriented, i.e., with IC pin I connected to the I position of the clip. A ground connection must be made between the circuit being tested and the checker to provide a common reference point for the lamp monitors. This can be done either by moving the matrix slider corresponding to the ground lead of the IC under test (if this is known) to GND (position 1), or by connecting a clip lead between one of the ground posts in the checker and a ground or common point on the board containing the IC being tested.

If the IC being checked is operating under its own power supply, the logic levels existing at all of its terminals will be displayed by the indicators directly. If the circuit is not self-powered, power can be supplied from the DIGI-DYNA-CHECK to the Vcc terminal of the IC via the matrix switch. Since up to I amp is available, the checker's power supply can "fire-up" a board containing many IC's: most digital IC's draw only a few milliamps each. However, current drain for most integrated circuits is dependent upon the output states and how often these states are changing-frequency. This happens because many gates draw extra current while changing state. Most manufacturers specify a maximum current consumption, and their literature should be consulted when in doubt.

One more word of CAUTION about using the internal +5 V supply for powering integrated circuits. The internal supply can only be used with IC's that are designed to operate at +5 volts. RTL (Resistor-Transistor Logic) circuits, for instance, require 3.6 volts and

can be damaged if connected to 5 volts. RTL units operating from their own power supply or from an external power source of the proper voltage *can*, nevertheless, be checked with the DIGI-DYNACHECK via the lamp monitors because their logic threshold region is within the threshold region of the lamp-driver circuits. A knowledge of what the logic states at the IC's terminals should be for a given circuit may be obtained from the spec sheets for the units under test.

It is possible, during in-circuit testing, to connect any of the internally available functions to the circuit under test. Thus, you can connect the STEP or CLOCK function to the input of a shift register, or a counter, or a flip-flop, and carry it through its paces under control of the DIGI-DYNA-CHECK. You can connect up to four IC terminals simultaneously (via positions A through D), to external components, or to a scope for monitoring input and output relationships.

#### **Out-of-circuit testing**

Out-of-circuit IC testing is performed much the same way as is done with a tube tester. The unit to be tested is plugged directly into the test socket, suitable input parameters are set (in the present case, via the matrix switch), and the result is read out on the front panel. In our case, we do not merely get a GOOD-?-BAD reading as with a tube tester, but rather, we obtain a lot more information about the IC under test. We are able to monitor all input and output logic levels simultaneously, and to compare them with each other and with expected levels based upon either a prior knowledge of the normal mode of operation of the logic type involved, (gate, counter, flip-flop, shift register, etc.) or from literature describing the specific unit being tested in which the normal input/output relationships are given. This latter type of data is generally contained in a TRUTH TABLE. This table indicates what the outputs should look like when certain combinations of input levels are present as well as what changes should occur when changes are made in the input levels.

Gates are the most basic logic sys-

tems. They can have, generally, either of two output states: a high or 1 level and a low or 0 level. The level or state that is present at the output of a particular gate depends upon the condition of the input(s) to the gate. The simplest gate, the INVERTER, or NOT gate always has an output state that is the opposite of its input (it has only one output and one input); a 1 at its input results in a 0 at its output, and vice versa.

Let's briefly look at truth tables for some of the more common types of logic building blocks (basic logic circuit types). The following table is a combined truth table for two-input NAND, AND, NOR, OR, and EXCLUSIVE-OR gates:

| INP | UTS | OUTPUTS |     |    |     |         |  |  |  |

|-----|-----|---------|-----|----|-----|---------|--|--|--|

| Α   | В   | NAND    | AND | OR | NOR | EXCL-OR |  |  |  |

| 0   | 0   | 1       | 0   | 0  | 1   | 0       |  |  |  |

| 0   | 1   | 1       | 0   | 1  | 0   | 1       |  |  |  |

| 1   | 0   | 1       | 0   | 1  | 0   | 1       |  |  |  |

| 1   | 1   | 0       | 1   | 1  | 0   | 0       |  |  |  |

|     |     |         |     |    |     |         |  |  |  |

Some generalizations may be made:

- For the first four types of gates, the output is at one condition for all input combinations except one.

- The NAND outputs are the opposite or inverse of the AND outputs for a given set of input conditions.

- The NOR outputs are the opposite or inverse of the OR outputs for a given set of input conditions.

- The EXCLUSIVE-OR gate is at one state if both inputs are identical and in the opposite state if the inputs are different. This property of the EXCLUSIVE-OR gate makes it useful as a digital comparator—for comparing two digital quantities or two digital states with each other.

Similar truth tables and general observations can be made for gates containing more than two inputs; the number of input combinations, of course, increases with the number of inputs involved.

Flip-flops represent the next most complex systems in digital circuitry. One widely used type is known as the J-K flip-flop. Unlike simple gates discussed above which have no memory, flip-flops remain in a given state even after the input conditions that put it into that state have been removed. Flip-flops often have two complementary outputs known as Q and not-Q (written Q). A J-K flip-flop has a "clock" input that serves as the trigger for the device. Output states are made to change by applying a pulse at the clock terminal. The states assumed by the Q and Q outputs depend upon the levels present at the J and K inputs immediately preceeding the clock pulse as well as the states of the Q and  $\overline{Q}$  outputs at that time. The normal transitions are summarized in the next table.

| At tir | ne, t     | At time, t + 1                                    |

|--------|-----------|---------------------------------------------------|

| J      | Κ         | QQ                                                |

| 0      | 0         | No change in state                                |

|        |           | (maintains whatever state was present at time, t) |

|        | _         | was present at time, t)                           |

| 1      | 0         | 1 0                                               |

| 0      | 1         | 0 1                                               |

| 1      | 1         | Assumes the inverse of                            |

|        |           | the output states that                            |

|        |           | were present at time, t                           |

| NOT    | □ · · · · | the time just before the                          |

NOTE: t is the time just before the "clock" pulse. t + 1 is the time just following

the "clock" pulse.

Now we're ready to apply what we've learned about the basic digital logic building blocks to checking digital IC's with the DIGI-DYNA-CHECK. We will select several IC's and carry them through their tests. The following table lists some of the more commonly used TTL (Transistor-Transistor Logic) integrated circuits with their internal terminal connections. We will look at several units listed in the table in order of increasing complexity, including an IN-VERTER, NAND, NAND with open-collector outputs, J-K flip-flop, and, finally, a decade counter.

|         |        | TABLE II                        |

|---------|--------|---------------------------------|

| Pin No. | Set to | Remarks                         |

| 7       | GND    | Power supply to the IC          |

| 14      | + 5 V  |                                 |

| 1, 2    | +5V    | Inputs to gate 1 at logical "1" |

| 4, 5    | + 5 V  | Inputs to gate 2 at logical "1" |

| 9, 10   | + 5 V  | Inputs to gate 3 at logical "1" |

| 12, 13  | + 5 V  | Inputs to gate 4 at logical "1" |

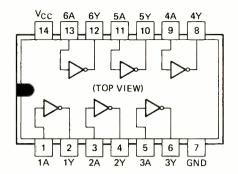

SN7404

SCHEMATIC (EACH INVERTER)

FIG. 2-THE SN7404. Basing diagram is at the top. Schematic of each inverter is also shown. There are six in this IC.

#### SN7404: Hex inverter

This 14-pin IC contains six separate inverters with their inputs and outputs wired as shown in the table below and in Fig. 2. Plug it into the test socket making certain that it is properly oriented, with its pin 1 in hole 1 of the socket. Connect pin 7 to GND and pin 14 to +5 V by moving matrix sliders corresponding to these pins to the positions indicated. This will provide operating power to the IC. Now set the sliders for terminals 1, 3, 5, 9, 11, and 13 (the six inputs) to +5 V (logical 1) and note the conditions of the lamps. All lamps corresponding to terminals that are connected to +5 V should be on (1) whereas all lamps corresponding to output terminals (2, 4, 6, 8, 10, and 12) should be off (0); we have already seen, in our discussion of gates, that IN-VERTER outputs should maintain states that are the inverse of their inputs. Try other combinations of input states and note that, if the IC is operating properly, all outputs will be the inverse of their respective inputs.

Thus, we can check the entire integrated circuit at the same time . . . all six inverters, simultaneously.

#### SN7400: Quad two-input nand gates

This IC contains four two-input NAND gates on a single chip. Here again, we will perform tests on all parts of the unit simultaneously. Plug the circuit into the test socket, properly oriented. The truth table for each of the four NAND gates is as was given earlier. Make the initial settings as per Table II

All input lamps should be at logical 1 (on) and all outputs should be at logical 0 (see truth table for a NAND gate).

Now change the settings for the in-

| NUMBER/TYPE        |     |      |      |       |     |      |     | IN NII | MBEF | 90  |     |     |     |     |    |            |        |

|--------------------|-----|------|------|-------|-----|------|-----|--------|------|-----|-----|-----|-----|-----|----|------------|--------|

| NOMBER/11FE        | 1   | 2    | 3    | 4     | 5   | 6    | 7   | 8      | 9    | 10  | 11  | 12  | 13  | 14  | 15 | 16         |        |

| SN7400-QUAD 2-IN   | IN  | IN   | OUT  | ΙŃ    | IN  | _    | GND | OUT    | IN   | IN  | OUT | iN  | IN  | vcc |    |            | SN7400 |

| NAND GATE          | 1A  | 1B   | 1    | 2A    | 2B  | 2    |     | 3      | 3A   | 3B  | 4   | 4A  | 4B  |     |    |            |        |

| SN7401-QUAD 2-IN   | OUT | IN   | IN   | OUT   | IN  | IN   | GND | IN     | IN   | OUT | IN  | IN  | OUT | vcc |    |            | SN7401 |

| NAND-O/C GATE      | 1   | 1A   | 1B   | 2     | 2A  | 2B   |     | 3A     | 3B   | 3   | 4A  | 4B  | 4   |     | Ī  |            |        |

| SN7404-HEX INVERT  | IN  | OUT  | IN   | OUT   | IN  | OUT  | GND | OUT    | 1N   | OUT | IN  | OUT | IN  | vcc |    |            | SN7404 |

| GATES              | 1_  | 1    | 2    | 2     | 3   | 3    |     | 4      | 4    | _ 5 | 5   | 6   | 6   |     |    |            |        |

| SN7430-8-IN NAND   | IN  | IN   | IN   | IN    | IN  | IN   | GND | OUT    | N/C  | N/C | IN  | IN  | N/C | VCC |    |            | SN7430 |

| GATE               | Α   | В    | С    | D     | E   | F    |     |        |      |     | G   | Н   |     |     |    |            |        |

| SN7442-4 TO 10     | OUT | OUT  | OUT  | OUT   | OUT | OUT  | OUT | GND    | OUT  | OUT | OUT | IN  | IN  | IN  | IN | VCC        | SN7442 |

| BCD DECODER        | 0   | 1    | 2    | 3_    | 4   | 5    | 6   |        | 7    | 8   | 9   | D   | C   | В   | Α  |            |        |

| SN7473 DUAL J-K    | CLK | CLR  | K    | VCC   | CLK | CLR  | J   | NQ     | Q    | K   | GND | Q   | NQ  | J   |    |            | SN7473 |

| M-S FLIP-FLOPS     | 1   | 1    | 1    |       | 2   | 2    | 2   | 2      | 2    | 2   |     | 1   | 1   | 1   |    |            |        |

| SN7474-DUAL D-EDG  | CLR | D    | CLK  | PRE   | Q   | NQ   | GND | NQ     | Q    | PRE | CLK | D   | CLR | vcc |    |            | SN7474 |

| TRIG FLIP-FLOPS    | _1_ | 1    | 1    | 1     | 1   | 1    |     | 2      | 2    | 2   | 2   | 2   | 2   |     |    |            |        |

| SN7480-GATED FULL  | B≑  | В    | C    | NC    | SUM | NSUM | GND | Α      | A    | Α*  | Α   | В   | В   | VCC |    |            | SN7480 |

| ADDER              |     | С    | n    | n + 1 |     |      |     | 1      | 2    |     | С   | 1   | 2   |     |    |            |        |

| SN7486-QUAD 2-IN   | IN  | IN   | OUT  | IN    | IN  | OUT  | GND | OUT    | IN   | IN  | OUT | IN  | IN  | vcc |    |            | SN7486 |

| EXCL-OR GATES      | 1A  | 1B   | 1    | 2A    | 2B  | 2_   |     | 3      | 3A   | 3B  | 4_  | 4A  | 4B  |     |    |            |        |

| SN7490-DEC CNTR-   | IN  | RST  | RST  | N/C   | VCC |      | RST | OUT    | OUT  | GND | OUT | OUT | N/C | IN  |    | — <b>—</b> | SN7490 |

| DIV BY 2+5         | B-D | 0-1  | 0-2  |       |     | 9-1  | 9-2 | C      | В    |     | D   | Α   | _   | Α   |    |            |        |

| SN7491-8 BIT SHIFT | N/C | N/C  | N/C  | N/C   | VCC | N/C  | N/C | N/C    | N    | GND | IN  | IN  | Q   | NQ  |    |            | SN7491 |

| REGISTER           |     | 11.5 | 11.5 | 11.5  |     |      |     |        | CP   |     | В   | A   |     |     |    |            |        |

| SN7492-DIV 12-CNTR | IN  | N/C  | N/C  | N/C   | VCC |      | RST | OUT    | OUT  | GND | OUT | OUT | N/C | IN  |    |            | SN7492 |

| DIV BY 2+6         | B-C |      |      |       |     | 0-1  | 0-2 | D      | С    |     | В   | Α   |     | A   |    |            |        |

ABBREVIATIONS:

IN-INPUT

OUT-OUTPUT GND-GROUND VCC-SUPPLY VOLTAGE

CLK-CLOCK CLR-CLEAR

Q-FLIP FLOP OUTPUT NQ-INVERSE Q ("NOT" Q)

PRE-PRESET INPUT N/C-NO CONNECTION RST-RESET

puts to correspond to the other input combinations shown in the truth table for a NAND gate to see if the outputs conform to those given.

# SN7401: Quad two-input nand gates with open collectors

Testing of these NAND gates is similar to that procedure already discussed above for the SN7400, except that these gates have open-collector outputs and require the addition of "pull-up" resistors to drive the indicator lamps. Pull-up resistors are normally connected between the outputs and +5 V. This is done in the DIGI-DYNA-CHECK as follows:

Move slider W to +5 V to bring +5 volts out to binding post W. Now, connect pins 1, 4, 10, and 13 (the NAND gate outputs) to binding posts A through D, respectively, via their matrix sliders. You can now connect the required resistors (approx. 1000 to 4000 ohms).

Connect  $V_{\rm cc}$  and ground and set the inputs as before (for the SN7400) observing the proper terminal connections for the SN7401, and carry the gates through their various input combinations as before.

#### SN7473: Dual J-K flip-flops

This integrated circuit contains two complete J-K flip-flops in a single package. For the sake of simplicity, and since both flip-flops operate identically, we will only go through the tests for one of them. After the IC has been properly inserted into the test socket, connect pin 4 to +5 V and pin 11 to GND to supply operating power to the circuit. Let's go through a manual test, first. Set pin 1 (CLOCK input) to the STEP position and pins 14 (J-input) and 3 (K-input) to one of the combinations shown in the truth table for a J-K flip-flop. Momentarily connect pin 2 (CLEAR) to GND and then to +5 V and leave it there. This is done to clear it, i.e., bring it to an initial state. Enter a "clock" pulse, manually, by depressing the STEP button one time only and releasing it. The outputs, Q and  $\overline{Q}$ , should react according to that which is given in the truth table for the particular combination of J and K inputs that you have entered. Clear the flip-flop again by momentarily grounding the CLEAR input (pin 2) and returning it to +5 V. Set the J and K inputs (pins 14 and 3, respectively) to a different combination of logic states and then enter a clock pulse. Check the result once again and compare it with the truth table. Try the other two J-K combinations, referring, again, to the table. You can also try entering several clock pulses for the 1, 1 combination of J-K inputs. The outputs should oscillate back and forth between two states. The second flip-flop in this IC can be checked out in a similar manner, either separately, or simultaneously with the first one, as above.

To operate the flip-flops automatically, at a rate of 50 kHz, for monitoring input/output relationships with a scope, use the INT CLOCK setting instead of the STEP setting for the clock input. Set the matrix sliders corresponding to the output terminals of interest to positions A through D and move the sliders W through Z to the same positions as the input terminals of interest and connect the scope to the binding posts. For every two clock pulses, you should see one square-wave pulse at either of the two outputs. The two outputs (Q and  $\overline{Q}$ ) should be 180° out of phase. A flip-flop is, thus a divide-by-two device.

The SN7490 contains four flip-

flops that are internally wired to form separate divide-by-two and divide-by-five counters. These can be operated either separately with their own individual inputs and outputs, or they can be wired, externally, together as a single divide-by-ten (decade) counter by connecting the output terminal of the divide-by-two section to the input terminal of the divide-by-five section and using input A (to the first flip-flop) as the decade input. When it is operated in this mode, the outputs are in BCD code; the four outputs have the values:

| Output: | Α   | В   | С       | D       |

|---------|-----|-----|---------|---------|

| Value:  | 20  | 21  | $2^{2}$ | $2^{3}$ |

|         | (1) | (2) | (4)     | (8)     |

BASING OF ALL IC's listed in the table on the preceding page. You'll want these diagrams handy when you set up your IC tester to check out any of these units.

SUM OUTPUTS

Thus the BCD-coded output of the decade counter is represented by the following conditions of the four flip-flop outputs:

| Number | Α | В | С | D |

|--------|---|---|---|---|

| 0      | 0 | 0 | 0 | 0 |

| 1      | 1 | 0 | 0 | 0 |

| 2      | 0 | 1 | 0 | 0 |

| 3      | 1 | 1 | 0 | 0 |

| 4      | 0 | 0 | 1 | 0 |

| 5      | 1 | 0 | 1 | 0 |

| 6      | 0 | 1 | 1 | 0 |

| 7      | 1 | 1 | 1 | 0 |

| 8      | 0 | 0 | 0 | 1 |

| 9      | 1 | 0 | 0 | 1 |

When the unit has counted ten input pulses, it automatically resets itself to zero and starts again. Let's now see how this IC is tested with DIGI-DYNA-CHECK.

### 1. As separate ÷ 2 and ÷ 5 counters—

Make the following initial settings:

| Pin No           | Set to                   | Remarks                                                                |

|------------------|--------------------------|------------------------------------------------------------------------|

| 10<br>5          | GND }<br>+5V }           | To supply power to the IC                                              |

| 2<br>3<br>6<br>7 | GND<br>GND<br>GND<br>GND | This deactivates the reset inputs to permit the flip-flops to function |

| 14<br>1          | STEP<br>STEP             | Input to the ÷2 counter Input to the ÷5 counter                        |

Momentarily move the sliders corresponding to pins 2, 3, 6, and 7 to +5 V, simultaneously, and then back to GND. This resets both counters to zero and allows input pulses to be counted. All output lamps should now be off (logical0). Depress the STEP button and release it to enter a single count pulse to both sections. Repeat this four more times, comparing the output logic states with those

| Input Pulses  |     |     |     |     |     |             |  |  |

|---------------|-----|-----|-----|-----|-----|-------------|--|--|

| Lamp No       | 1st | 2nd | 3rd | 4th | 5th | Remarks     |  |  |

| 12 (Output A) | 1   | 0   | 1   | 0   | 1 , | ÷ 2 counter |  |  |

| 9 (Output B)  | 1   | 0   | 1   | 0   | 0 ) |             |  |  |

| 8 (Output C)  | 0   | 1   | 1   | 0   | o > | ÷ 5 counter |  |  |

| 11 (Output D) | 0   | 0   | 0   | 1   | 0)  |             |  |  |

shown in the table above:

## 2. As a single ÷10 (decade) counter-

Make the following changes in the matrix switch settings:

| Move Pin No | to Position |  |

|-------------|-------------|--|

| 1           | Α           |  |

| 12          | Α           |  |

#### Remarks

This disconnects input of the  $\div 5$  unit from STEP and connects a jumper (bus A) between the  $\div 2$  output and  $\div 5$  input.

Reset all counters as described above and then enter ten pulses, noting whether the outputs correspond to the 0 thru 9 BCD code given earlier. Here again, as in our earlier discussion involving the flip-flop tests, the use of the automatic INTERNAL CLOCK function instead of the manual STEP function permits you to use a scope to monitor input/output logic states and waveforms.

#### Checking current drain IC

It's a simple matter, with the DIGI-DYNA-CHECK, to route +5 volts to the V<sub>cc</sub> terminal of an IC, indirectly, via a pair of binding posts. An ammeter connected to the posts will then be in series with the power supply to the circuit and will indicate current drain. This is accomplished by moving one of the sliders W through Z to +5 V, thus bringing +5 volts out to a binding post. Moving the slider corresponding to the IC's V<sub>cc</sub> terminal to one of the positions A through D will bring it out to a binding post. Current drain can be monitored continuously while performing other tests on the IC.

We have seen that there are many ways in which the DIGI-DYNA-CHECK can be used to test digital ICs. A complete description of all of its uses is beyond the scope of this article. The use of a matrix switch together with the input/output binding posts makes the checker almost universal. Any IC terminal can be connected to any function, either internally or externally. Where needed, special adapters can be made to accommodate package types other than 14- and 16-pin DIPs. Thus, you might say that the DIGI-DYNA-CHECK is as close to obsolete-proof as you can get!

The multitude of ways in which this tester can be applied to digital IC testing is limited only by your imagination!

Many readers have already asked "Where do I buy parts to build my own Digital IC Tester, as described in the May 1972 issue?" The answer to that query was supposed to have appeared at the end of the parts list last month. As you must know by now, it did not. Therefore, we are presenting here, the listing that was omitted last issue."

The following kits of parts are available from The Electronetics Co. Inc., P.O. Box 278, Cranbury, N.J. 08512.

bury, N.J. 08512.

DDC-1 consisting of Q1 thru Q36; D1 thru D5; bridge rectifier; IC1; matrix switch and DIP test clip: \$54.50, including postage and insur-

DDC-2 consisting of a manual listing pin connections for many popular integrated circuits, useful for programming the DIGI-DYNA-CHECK: \$2.00 including postage.

### cb radio call light

CB transceivers are often installed on motorcycles, sports cars, snowmobiles and in countless other noisy locations. The high noise level may cause an operator to miss an incoming call. An article in *Electron* magazine (Toronto, Ont.) shows how a call light can be added to indicate that a signal is being received.

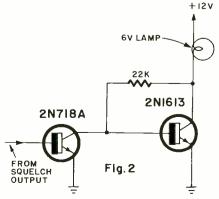

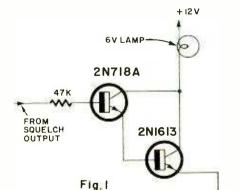

The circuit in Fig. I can be added to receivers that produce a negative-going voltage at the squelch output when a signal comes on the air. The lamp turn-on voltage depends on the setting of the squelch control. The indicator circuit can also be driven by the emitter voltage of an rf transistor if this voltage swings negative on an incoming signal. With this arrangement, the lamp comes

on with a S4-S6 signal. The circuit in Fig. 2 can be used in sets where an in-

coming signal develops a positive-going voltage.